即可将网页分享至朋友圈

12月6日,我校英才实验学院(通信工程专业)2017级本科生夏子寒在通信抗干扰国家级重点实验室陈杰男副教授(博导)指导下,在《IEEE Transactions on Circuits and Systems I: Regular Papers》期刊(中科院2020分区大类一区,TOP期刊)上发表题为“Neural Synaptic Plasticity-Inspired Computing: A High Computing Efficient Deep Convolutional Neural Network Accelerator”的论文。夏子寒为该论文第一作者,陈杰男副教授为通讯作者,电子科技大学为第一作者单位。

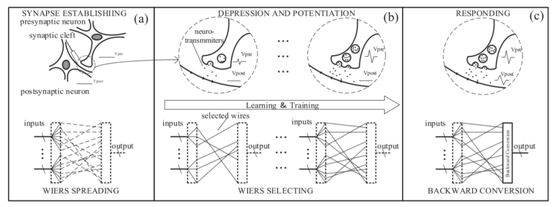

Fig. 1. Model mapping: the NSPC and the neural synaptic plasticity.

(a) wires spreading unit and the establishment of synaptic structures.

(b) wires selecting unit and the synaptic strength’s potentiation and depression.

(c) backward conversion unit and the response of synapse.

本文中,研究者们尝试用电路模拟人脑突触结构,以解决目前深度学习硬件高计算复杂度问题。传统的解决方法多从浮点数定点化、权值与激活值的低比特量化、网络连接的稀疏性等方向进行探索。然而,鲜有学者从更加有生物解释性的角度去探索目前深度学习硬件电路的低复杂度实现方案。

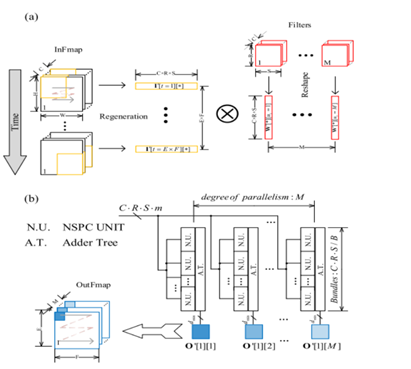

Fig. 2. Parallel matrix multiplication scheme. (a) the visualization of data mapping, (b) matrix multiplication with the parallel bundle optimization.

综合考虑上述问题,夏子寒等研究者们提出了一种受启发于人工神经网络的生物本质属性,即神经元突触可塑性,使用电路连线的密度来模拟神经网络的权值绝对值大小,实现在概率意义下的近似计算——Neural Synaptic Plasticity-Inspired Computing(NSPC)。研究者们经过严格的数学推导,把乘累加(MAC)的计算分为了前向转换、概率选择、反向变换三个步骤,并且分别设计了线扇出单元、线选择单元、反向变换单元进行实现。在此基础上,研究者们把深度卷积神经网络中的卷积运算转换为矩阵乘法运算,并且使用NSPC进行实现。此外,通过联合设计神经网络结构与数据流,实现了低复杂度、高吞吐量的深度卷积神经网络加速器。相比传统定点数实现,具有2.77倍的面积效率和2.25倍的能量效率。

夏子寒同学于2019年春加入陈杰男副教授带领的“超新思维”团队。今年1月他在IEEE电路与系统旗舰会议ISCAS上还发表一作论文,目前他正在进行5G LDPC概率解码器芯片设计。陈杰男老师近年已指导多名本科生发表高水平学术会议和SCI期刊论文。他带领的超新思维团队致力于以深度学习为基础探索毫米波MIMO、波束成形、自动驾驶、智能EDA设计、和数字信号处理技术。

相关链接:

论文链接:https://ieeexplore.ieee.org/document/9281377

超新思维团队网站:http://novamind-uestc.com/home

编辑:何易虹 / 审核:林坤 / 发布:陈伟