即可将网页分享至朋友圈

近期,信息与通信工程学院周军教授团队在类脑智能算法和芯片方向的成果分别发表在顶级会议AAAI和VLSI Symposium。

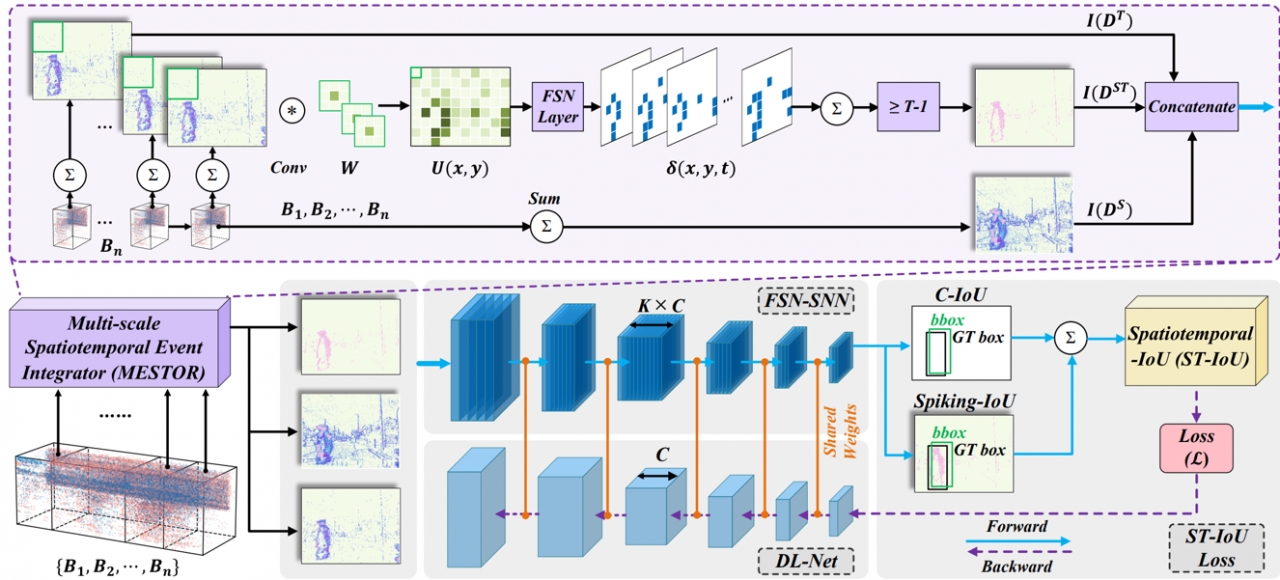

其中,类脑智能算法成果《CREST: An Efficient Conjointly-trained Spike-driven Framework for Event-based Object Detection Exploiting Spatiotemporal Dynamics》发表在人工智能领域顶级会议AAAI 2025。该论文通讯作者为周军教授,周军教授指导的博士生毛睿昕和硕士生申遨宇为共同第一作者。该工作提出了一种类脑事件驱动目标检测算法框架。事件相机具有高时间分辨率、宽动态范围和低功耗,非常适合高速和弱光环境下的目标检测。脉冲神经网络SNN在事件驱动目标识别与检测中具有优势,但现有方法因训练效率低下,存在梯度消失和计算复杂度高的问题,尤其在深层SNN中表现突出。此外,当前SNN框架难以有效处理多尺度时空特征,导致数据冗余和精度下降。为解决上述问题,本文提出了CREST,即一种支持联合学习的脉冲驱动框架,用于挖掘事件驱动目标检测中的时空动态特性。结合学习规则可以加速SNN训练并缓解梯度消失,同时支持两种训练模式,便于在不同硬件平台上灵活高效地部署。此外,该框架还包括脉冲驱动的多尺度时空事件特征提取器(MESTOR)和时空IoU损失函数(ST-IoU)。实验结果表明,CREST在三个数据集上实现了出色的目标识别和检测性能,并大大提高了计算能效,为面向硬件实现的类脑事件驱动目标检测算法提供了一种高效的解决方案。

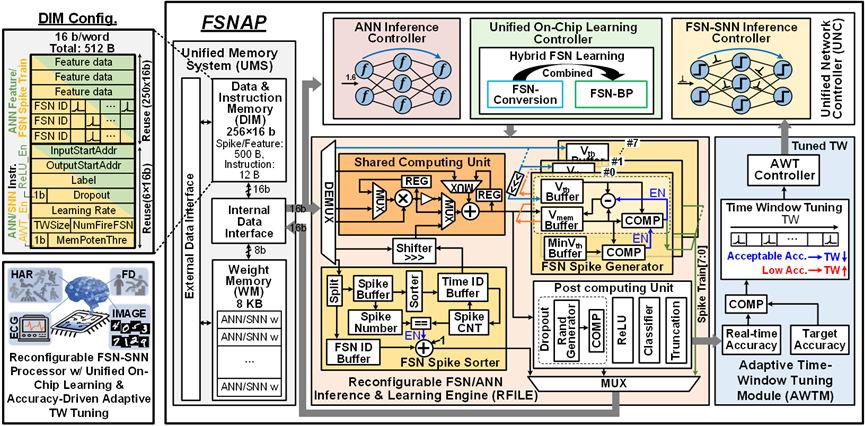

类脑智能芯片成果《FSNAP: An Ultra-Energy-Efficient Few-Spikes-Neuron based Reconfigurable SNN Processor Enabling Unified On-Chip Learning and Accuracy-Driven Adaptive Time-Window Tuning》发表在芯片设计领域顶级会议VLSI Symposium 2024,是电子科技大学在人工智能芯片领域的首篇VLSI Symposium顶会论文。该论文的通讯作者为周军教授,周军教授指导的博士生毛睿昕为第一作者。该工作提出了一种极高能效的类脑学习/推理一体化芯片架构,并完成了芯片流片验证。SNN处理器因其低功耗特性被视为人工神经网络(ANN)处理器的高能效替代方案。基于泄漏整合放电(LIF)神经元,需较大时间窗口和大量脉冲以实现高精度,导致计算能耗高、时延长。这些处理器通常仅支持基于脉冲的反向传播学习或ANN到SNN的转换学习,灵活性受限。此外,大多数处理器还使用固定的编码时间窗,适应性差,能效较低。为解决上述问题,本研究提出了一种基于少量脉冲神经元(FSN)模型的高能效SNN处理器——FSNAP, 它具有:(1)基于FSN的可重构推理与学习架构,通过跳时间步脉冲累加技术和并行脉冲生成技术,提升计算效率并降低时延;(2)统一片上学习架构,支持低复杂度的多种在线学习模式,提升推理准确率与灵活性;(3)基于准确率驱动的自适应时间窗调整技术,在保证高精度的同时降低能耗与延迟。FSNAP采用55nm CMOS工艺,在相同或相似规模任务中,相较于现有SOTA设计,能效和加速比都显著提高,同时保证了较高的准确率。

图1 CREST算法的整体框架

图2 FSNAP芯片总体架构图

传统的人工神经网络(ANN)是人脑高度简化的数学抽象,使用连续的幅度表示信息,尽管准确率很高,但是需要大量的乘加运算,因此能耗很大。脉冲神经网络(SNN)仿照了人脑事件驱动的机制进行计算,使用稀疏脉冲串的频率和发放时间来表示不同的信息,具有计算量低,能耗低的特点。现有的类脑计算芯片主要有几个问题:1. 几乎都基于泄露-积分-发射(LIF)神经元,这种神经元的编码效率很低,通常需要很大的编码时间窗,发放很多的脉冲才能达到很高的准确率,这会增加能耗和时延。2. 仅支持固定编码时间窗来进行前向推理,适应性较差,能效较低。3. 仅支持单一的SNN学习方式(基于脉冲的反向传播和ANN到SNN转换的方法),缺乏针对不同应用的适应性。针对以上问题,团队设计了超低能耗的FSNAP芯片,该芯片具有可重构的SNN推理和学习架构,支持跳时间步脉冲累加技术以及并行的脉冲发放技术,从而实现高能效、低延时。同时,提出了一种准确率驱动的自适应调窗技术来进一步降低能耗、时延同时保持高准确率。此外,设计了统一的在线学习架构,支持3种在线学习模式,从而增加芯片针对不同应用的适应性。芯片采用55nm制造,与现有的先进设计在相同或相似的任务上相比,能效和加速比都显著提高。

周军教授团队致力于端侧AI算法与芯片协同设计,团队发表了电子科大在AI芯片领域今为止的全部四篇ISSCC(芯片设计领域奥林匹克会议),以及电子科大在AI芯片领域的首篇HPCA(体系结构领域顶级会议)、VLSI(芯片设计领域顶级会议)、CICC(芯片设计领域顶级会议)和DAC(芯片设计自动化领域顶级会议)文章,结合算法与芯片协同创新,设计并实现了面向视觉感知、声音感知、智能穿戴等应用的多款超低功耗端侧AI芯片,在满足准确率、实时性需求的同时,达到了国际同类设计最低能耗。相关技术已转化应用到中科曙光、华大电子、深圳中微半导体等知名公司,以及相关科研单位,服务国家重大需求和社会经济发展。

编辑:张闻起 / 审核:李果 / 发布:陈伟